Acqua technical documentation Buy

Set a unique eth0 MAC address on Acqua reading the on-board Microchip AT24MAC402 EEPROM

An Microchip AT24MAC402 chip is mounted by default on each Acqua A5 SoM.

This provides:

- An unique 128-bit serial number

- An unique and valid EUI-48 address

- 2-Kbit of EEPROM

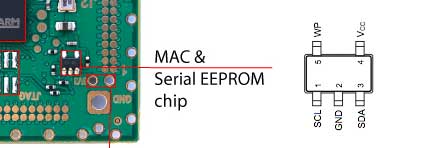

Here is where is located the chip:

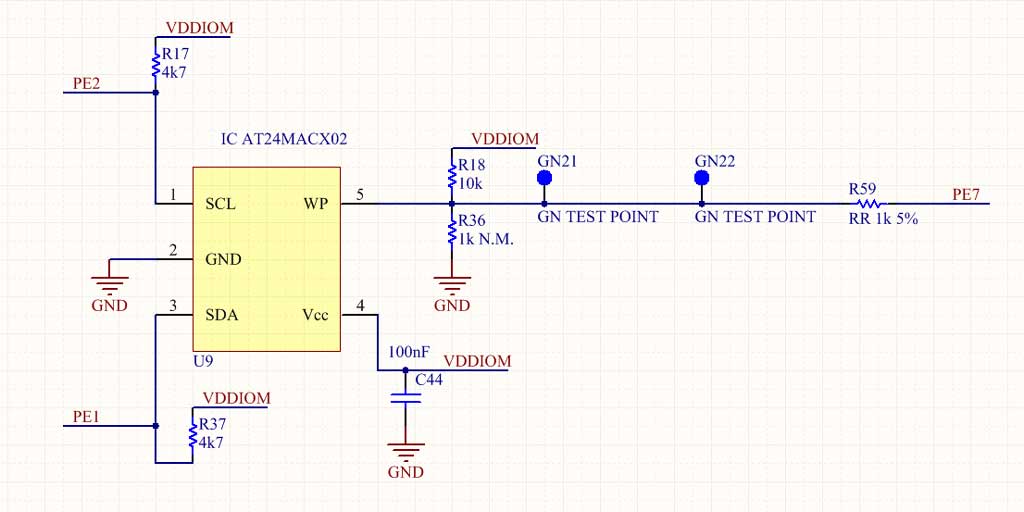

and this is how is wired at the SAMA5D3x MPU:

To implements the I2C bus used to talk with the chip we have used some generic GPIO thus leaving the hardware I2C bus free for the user application.

This are the GPIO lines used:

| Signal | Description | Atmel Line | Acqua pin |

|---|---|---|---|

| SDA | I2C data | PE1 | N.A. |

| SCK | I2C clock | PE2 | N.A. |

| WP | Write protect | PE7 | N.A. |

The I2C bus is managed by a bit banging Linux driver and activated by the device tree file in that way:

/* Bit banging I2C wired on the Atmel MAC chip */

i2c3@ {

compatible = "i2c-gpio";

gpios = <&pioE 1 0 /* SDA */

&pioE 2 0 /* SCK */

>;

i2c-gpio,delay-us = <4>; /* ~178 kHz */

#address-cells = <1>;

#size-cells = <0>;

};

The I2C address is: 0x58

On this repository are available two simple utilities written in C language to read the MAC address and the Serial Number from user space:

Here is an example to use them:

sudo ./at24mac

FC:C2:3D:0D:A6:EB

sudo ./at24serial

0A70080064100460746CA000A0000000

Set the MAC address at bootstrap using a dts definition

With this method is possible to set the MAC address on eth0 during the boot time using just a device tree binding. When this method is active the EEPROM is not available from user space.

macb1: ethernet@f802c000 {

compatible = "atmel,sama5d3-macb", "cdns,at91sam9260-macb", "cdns,macb";

status = "okay";

phy-mode = "rmii";

#address-cells = <1>;

#size-cells = <0>;

nvmem-cells = <ð0_addr>;

nvmem-cell-names = "mac-address";

phy0: ethernet-phy@1 {

interrupt-parent = <&pioE>;

interrupts = <30 IRQ_TYPE_EDGE_FALLING>;

reg = <1>;

};

/*ethernet-phy@1 {

reg = <0x1>;

};*/

};

i2c3@ {

compatible = "i2c-gpio";

sda-gpios = <&pioE 1 (GPIO_ACTIVE_HIGH|GPIO_OPEN_DRAIN)>;

scl-gpios = <&pioE 2 (GPIO_ACTIVE_HIGH|GPIO_OPEN_DRAIN)>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c3_gpio>;

i2c-gpio,delay-us = <4>; /* ~178 kHz */

#address-cells = <1>;

#size-cells = <0>;

/* EEPROM contains the eth0 MAC address */

eeprom@58 {

compatible = "atmel,24mac402";

pagesize = <256>;

read-only;

reg = <0x58>;

#address-cells = <1>;

#size-cells = <1>;

eth0_addr: eth-mac-addr@9A {

reg = <0x0 0x06>;

};

};

};

pinctrl@fffff200 {

board {

pinctrl_i2c3_gpio: i2c3-gpio {

atmel,pins =

<AT91_PIOE 1 AT91_PERIPH_GPIO AT91_PINCTRL_NONE

AT91_PIOE 2 AT91_PERIPH_GPIO AT91_PINCTRL_NONE>;

};

}

}

Inside the Kernel menuconfig these two driver are requested:

CONFIG_EEPROM_AT24=y

CONFIG_I2C_GPIO=y

Links

- GitHub repository of at24mac utility

- Atmel AT24MAC402 datasheet

- https://git.kernel.org/pub/scm/linux/kernel/git/stable/linux.git/tree/Documentation/devicetree/bindings/eeprom/at24.txt?h=v4.19.128

- https://git.kernel.org/pub/scm/linux/kernel/git/stable/linux.git/tree/Documentation/devicetree/bindings/net/ethernet.txt?h=v4.19.128

- https://git.kernel.org/pub/scm/linux/kernel/git/stable/linux.git/tree/arch/arm/boot/dts/da850-lego-ev3.dts?h=v4.19.128#n256

Credits

Many thanks to Antonio Galea for his help to find this solution https://github.com/ant9000

Systems designer, webmaster of www.acmesystems.it and founder of Acme Systems srl

Personal email: tanzilli@acmesystems.it

Web pages: https://www.acmesystems.it --- https://www.acmestudio.it

Github repositories: https://github.com/tanzilli --- https://github.com/acmesystems

Telegram group dedicated to the Acme Systems boards: https://t.me/acmesystemssrl